Scientific Journal of Impact Factor (SJIF): 4.72

# International Journal of Advance Engineering and Research Development

# Volume 4, Issue 11, November -2017

# Crosstalk Modeling and Analysis of Coupled RLC Interconnect for Signal Integrity

Bhattu.HariPrasad Naik<sup>1</sup>, Chandra Sekhar Paidimarry<sup>2</sup>

<sup>1,2</sup>, Dept. of ECE, UCE, Osmania University, Hyderabad, Telangana, India.

**Abstract**— With the technology advancements in the field of chip fabrication, the signal clock rates and data-rates are in several Giga-Hertz ranges. Simultaneously, signal rise times (edge rates) are in Pico-seconds range. On-chip interconnects on a multilayer board stack-up plays a vital role and constitute as major source of circuit delay than gate delays. This is because of decrease of trace width and various devices parasitic's on the chip. These can cause several implications such as electro-magnetic (EMI) issues in the designs. These problems can pose several design challenges to the designers with the Signal Integrity problems such as ringing, double clocking, non-monotonicity and performance degradation of designs. Typically, there are numerous analytical and numerical approaches used for the analysis of high speed interconnects. Each approach is different from the other in different domains of evaluation. Here, crosstalk voltage modeling and analysis of coupled RLGC models of interconnects with transient analysis in time domain is proposed. Transient analysis of lumped, coupled and distributed models of RLC interconnects is performed and performance metrics delays, average power, PDP and crosstalk voltages are measured. Hence, accurate modeling and validation of interconnect models is essential for the successful transmission of signals without ringing, crosstalk and EMI problems. These reduce the propagation delays and increase the overall circuit performance in-terms of speed.

Index Terms— Microstrip, Interconnect/trace, RLC, EMI, Crosstalk, Far End Crosstalk(FEXT), Near End Crosstalk(NEXT), Signal Integrity(SI), Delays, lumped, PDP,

### I. INTRODUCTION

In the deep-submicron (DSM) regime, high speed designs have faster edge rates signals and switching fast characteristics. Advancements in the chip fabrication technology, present high speed logics and designs are operating at much higher speed. The clock rates of the signal in high speed (>10MHz) designs have reached the GHz range and edge rates of the signal droped below 100pico-seconds range (e.g. DDR2, DDR3 and DDR4 designs) and signal frequency content of digital signals have extended to  $\approx$ 10GHz. In addition, designs on IC's are becoming more complex, complicated with decreased trace widths and smaller geometries. On a multilayer board stack-up, the effects of increase in frequency (GHz), decrease of trace widths and edge rates of the signals are always posing challenges to the designers with several critical signal integrity problems. These problems of SI are directly related to dV/dt or dI/dt, fast rise times that significantly worse some of the noise phenomena: power/ground switching noise, crosstalk, ringing, reflections and over/shoot. Many of problems of SI are electromagnetic in nature referred as EMI/EMC. These can degrade the overall performance of the system. So, it becomes essential to understand, where these problems of SI come from, analyze them and solve the problems at the early stage of design else the process of solving is time taking and cost effective. The fundamental goal of SI is to ensure high speed, reliable data transmission without ringing, crosstalk, double clocking, nonmonotonicity etc.SI is the measure of quality of signal (QoS), determined by quality (shape with thresholds) and arrival time of the signal. The signal timing depends on delays which in-turn depends on the physical length of interconnects, that the signal needs to propagate through. The designers must ensure the reliability of the designs by highlighting the problems of SI and EMI. Hence, thereby increases the quality of signal transmission that are high speed, reliable to obtain optimum performances from the designs. Interconnects constitute as dominant source of circuit delay than gate delays [1]. Depending on the physical length, often interconnects on the IC are modeled as distributed model with resistance, capacitance and inductance parasitic's. Interconnect delays is playing a vital role in circuit design and performance.

In a complicated multi-layered high speed interconnect system designs, propagation delays and signal coupling greatly affects circuit performances and lowers the yield of IC chips. A proper care needs to be taken regarding critical interconnects spacing, dimensions, layouts, and device parasitic's etc., prior to design. On a multilayer board stack-up, crosstalk is referred as the undesired voltage imparted from a aggressor line to a adjacent trace/interconnect (victim). Magnitude of crosstalk voltage induced in to a victim line is a function of rise time, trace geometry and type of terminations used.

Major impacts of cross talk in high speed designs are:

(a) Crosstalk induces timing delays that change the signal propagation time, and in-turn leads to setup/hold time failures.(b) Crosstalk induces glitches at the output, this causes voltage spikes on interconnect, results in false logic.

Hence, an accurate interconnect modeling, estimate and characterization of the crosstalk peak noise in interconnects is therefore very crucial for today's high speed designs. Model characterization is performed using transient analysis in time domain. The performance metrics of coupled lumped and distributed RLC models are evaluated. The objective of this work is to model and analyze the crosstalk coupling noise between the aggressor(s) and a victim line of a coupled RLGC

interconnects. Delay modeling of lumped model of RLC is presented in section-2. Subsequently crosstalk modeling of coupled interconnects in section-3. Crosstalk analysis of distributed interconnect model is presented in section-4 then followed by conclusion in section-5.

#### II. DELAY MODELING OF LUMPED RLC INTERCONNECT

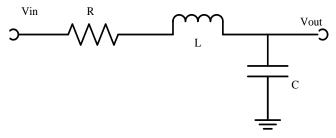

For SI analysis, interconnect/trace on a chip are either modeled as lumped or distributed models of transmission lines that serves as medium of sending signals. The propagation delay along the trace depends on circuit parasitic's and on the physical length of trace. Delay modeling of lumped model of RLC interconnect is shown in Figure.1. Here, voltage along both ends of trace changes instantaneously with propagation time(tp>>pD) neglected. But in a distributed model, the signal propagation time(tp) is considered along with length of the trace.

Fig. 1. Model of RLC Interconnect.

Apply the KVL to the RLC model of interconnect shown in Fig.1. Assume that i(t) be the current flowing in the RLC model which yields equation (1):

$$V_i(t) = V_R + V_L + V_C \tag{1}$$

$$V_i(t) = iR + L\frac{d}{dt}i(t) + \frac{1}{C}\int i(t)dt$$

$$V_i(t) = RCV_C(t) + LC\frac{d}{dt}V_C(t) + V_C(t)$$

<sup>(2)</sup>

Differentiate the equation (2) w.r.t to t yields

$$\frac{d}{dt}V_{i}(t) = C\frac{d}{dt}V_{C}(t)R + LC\frac{d^{2}}{dt^{2}}V_{C}(t) + V_{C}(t)$$

$$\frac{1}{LC}\frac{d}{dt}V_{i}(t) = \frac{R}{L}\frac{d}{dt}V_{C}(t) + \frac{d^{2}}{dt^{2}}V_{C}(t) + \frac{V_{C}(t)}{LC}$$

(3)

Since the obtained equation (3) is in time domain, use Laplace Transforms to covert from time domain to frequency domain for easy analysis.

$$\frac{1}{LC}V_{i}(s) = V_{C}(s)\left[s^{2} + \frac{R}{L}s + \frac{1}{LC}\right]$$

$$\frac{V_{C}(s)}{V_{i}(s)} = \frac{1/LC}{s^{2} + sR/L + 1/LC}$$

The transfer function of lumped model of RLC interconnects in frequency domain is given by second order equation (4):

$$H(s) = \frac{1/LC}{s^2 + sR/L + 1/LC}$$

(4)

The standard second order characteristic transfer function is given by equation (5).

$$H(s) = \frac{\omega_n^2}{s^2 + 2\xi\omega_n s + \omega_n^2}$$

(5)

On comparing the second order transfer function of RLC model i.e. equation (4) with the standard form of characteristic equation (4), we obtain the parameters such as angular frequency( $w_n$ ) and damping factor( $\xi$ ).

$$\omega_n^2 = \frac{1}{LC}$$

,  $2\xi\omega_n = \frac{R}{L}$

Delay ( $\tau$ ) of a lumped model of RLC interconnects is defined by the R, L, and C parasitic elements and is given by (6):  $\tau = 2L/_{-}$

$$\tau = \frac{2L}{R}$$

(0)

Approximate delay ( $\tau$ ) for distributed models of RLC interconnect of n<sup>th</sup> stage is given by (7).

$$\tau = \frac{2L}{R} + \frac{R^2 + RL + 2L}{R} + ... + \frac{nR^2 + nRL + 2L}{R}$$

(7)

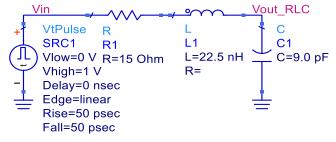

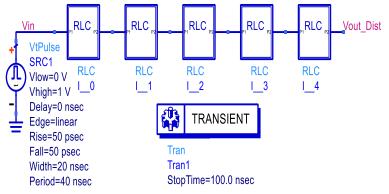

Figure.2 shows the transient analysis of the lumped model of RLC interconnect with the element parameters:  $R=15\Omega$ , L=22.5nH and C=9.0pF. Transient analysis is performed with a pulse as input with edgerate(rise, falltime) equals 50ps and period of pulse is 40ns. Here, RLC interconnect/ trace is assumed as a microstrip on a PCB. The length of the

trace/interconnect is L=3 inch, width W=8.0 mils, Dielectric height H=6.0 mils with a dielectric constant  $\varepsilon_r = 4.3$ . The characteristic impedance of interconnect is Z<sub>0</sub>=50Ω and the delay through the trace is td=448ps.

Fig. 2. Transient analysis of RLC Interconnect.

The transient response of 3 inch RLC interconnect is shown in Fig.3. Response shows that ringing is present at the output and this is due to the inductance (L) effect at high frequencies.

Fig. 3. Transient Response of RLC Interconnect.

#### III. CROSSTALK MODELING OF COUPLED INTERCONNECTS

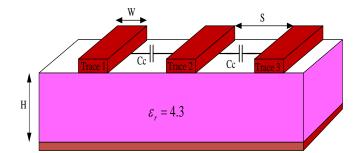

A PCB stackup is a multilayer board with many signal traces, vias and power planes(Vdd, Gnd) on it. At high frequencies interconnect/trace on a PCB are often modeled as transmission lines i.e. microstrip, stripline, etc with various dielectric materials used as substrates. The signal propagates through the trace at a speed of 6''/1ns which equals 165ps/inch approximately. A model of coupled traces is shown in Fig.4.

Fig. 4. Coupled model of trace/interconnect on a substrate.

On a multilayer board stack-up, crosstalk coupling happens when two signal traces/interconnects are running side by side to each other for some significant length i.e. data line. Crosstalk is generated between the traces due to coupling( $C_C$ ) and energy gets coupled from one trace(aggressor) to the adjacent trace(victim). Crosstalk increases with fast edge-rates(<100ps) and ringing thereby increasing di/dt. Crosstalk problems can be solved by placing the signal traces in close proximity to the (Vdd, Gnd) planes, use of guard traces and increase copper pour on the board to decrease current density. A relationship between trace width(W) and impedance( $Z_0$ ) of the trace/interconnect is given as (8):

$$Width(W)\alpha \frac{1}{Z_0}$$

(8)

High speed designs that are operating at high frequencies and fast edge-rates, crosstalk effect between traces/interconnects is an undesired effect that can cause several SI problems. Therefore, accurate crosstalk modelling between coupled interconnects and characterization is very essential. Crosstalk can affect the mutual inductance (M) as well as coupling capacitance (Cc=2.0pF) between interconnects.

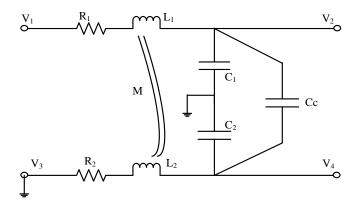

Fig. 5. Model of Coupled RLC Interconnect.

Figure.5 is used for theoretical modeling and analysis of crosstalk voltage in a coupled RLC interconnects. Analysis is performed with assumption V3=0 (Gnd) and the coupling coefficient between the inductors L1 and L2 is K=0.2. The crosstalk voltage induced by aggressor line on to Victim line are of two kinds i.e. Far End Crosstalk (FEXT) at V4 as output and Near End Crosstalk (NEXT) at V3 are estimated for a coupled RLC interconnect model shown in Fig.5. Now applying the nodal analysis to coupled RLC model of interconnect shown in Fig.5.

$$\frac{V_2 - V_1}{(R_1 + sL_1)} + \frac{V_2}{1/sC_1} + \frac{V_2 - V_4}{1/sC_c} = 0$$

(9)

$$V_{2}\left[\frac{1}{(R_{1}+sL_{1})}+sC_{1}+sC_{c}\right] = \frac{V_{1}}{(R_{1}+sL_{1})}+V_{4}*sC_{c}$$

$$V_{2}\left[(1+sRC_{1}+sRC_{2}+s^{2}LC_{2}+s^{2}LC_{2})\right] = V_{1}+V_{2}*(sRC_{2}+s^{2}LC_{2})$$

$$V_{2}\left[(1+sRC_{2}+s^{2}LC_{2}+s^{2}LC_{2})\right] = V_{2}+V_{2}*(sRC_{2}+s^{2}LC_{2})$$

$$V_{3}\left[(1+sRC_{2}+s^{2}LC_{2}+s^{2}LC_{2})\right] = V_{2}+V_{2}*(sRC_{2}+s^{2}LC_{2})$$

$$V_{3}\left[(1+sRC_{2}+s^{2}LC_{2}+s^{2}LC_{2})\right] = V_{2}+V_{2}*(sRC_{2}+s^{2}LC_{2})$$

$$V_{2}[(1+sR_{1}C_{1}+sR_{1}C_{c}+s^{2}L_{1}C_{1}+s^{2}L_{1}C_{c})]=V_{1}+V_{4}*(sR_{1}C_{c}+s^{2}L_{1}C_{c})$$

(10)

$$\frac{V_4 - V_2}{1/sC_C} + \frac{V_4}{(R_2 + sL_2)} + \frac{V_4}{1/sC_2} = 0$$

(11)

$$V_{4}\left[\frac{1}{(R_{2}+sL_{2})}+sC_{2}+sC_{C}\right]=V_{2}*sC_{C}$$

$$V_{4}=\frac{sR_{2}C_{C}+s^{2}L_{2}C_{C}}{\left[(1+sR_{2}C_{C}+sR_{2}C_{2}+s^{2}L_{2}C_{C}+s^{2}L_{2}C_{2}\right]}*V_{2}$$

(12)

The output voltage V<sub>2</sub> of the aggressor trace w.r.t input voltage V<sub>1</sub> is obtained by substitution of equation (12) in (10).  $V_2[(1+sR_1C_1+sR_1C_c+s^2L_1C_1+s^2L_1C_c)] = V_1 + \frac{(sR_1C_c+s^2L_1C_c)(sR_2C_c+s^2L_2C_c)}{(sR_1C_c+s^2L_1C_c)(sR_2C_c+s^2L_2C_c)} * V_2$

$$V_{2}\left[\frac{\left[1+sR_{1}C_{1}+sR_{1}C_{C}+s^{2}L_{1}C_{1}+s^{2}L_{1}C_{C}\right]^{\ast}\left[1+sR_{2}C_{1}+sR_{2}C_{C}+s^{2}L_{2}C_{2}+s^{2}L_{2}C_{C}\right]^{\ast}}{\left(1+sR_{2}C_{1}+sR_{2}C_{c}+s^{2}L_{2}C_{2}+s^{2}L_{2}C_{C}\right)}\right]^{-\left[sR_{C}+s^{2}L_{2}C_{2}+s^{2}L_{2}C_{C}\right]^{\ast}}\right]^{2}V_{2}\left[\frac{\left[1+s(R_{1}C_{1}+R_{2}C_{2}+R_{2}C_{2}+s^{2}L_{2}C_{2}+s^{2}L_{2}C_{2}\right)-\left(sR_{2}C_{2}+s^{2}L_{2}C_{2}+s^{2}L_{2}C_{2}\right)}{\left(1+sR_{2}C_{1}+sR_{2}C_{1}+s^{2}L_{2}-s^{2}L_{2}C_{2}\right)}\right]^{-\left[sR_{C}-s^{2}L_{2}C_{2}+s^{2}L_{2}C_{2}\right]}\right]^{2}V_{2}}{\left[r_{1}+s(R_{1}C_{1}+R_{2}C_{2}+R_{1}C_{C}+R_{2}C_{C}+s^{2}L_{2}C_{1}C_{2}+R_{1}R_{2}C_{1}C_{2}+R_{1}R_{2}C_{1}C_{2}+R_{1}R_{2}C_{1}C_{2}+R_{1}R_{2}C_{1}C_{2}+R_{1}R_{2}C_{1}C_{2}+R_{1}R_{2}C_{1}C_{2}+R_{1}R_{2}C_{1}C_{2}+R_{1}R_{2}C_{1}C_{2}+R_{1}R_{2}C_{1}C_{2}+R_{1}R_{2}C_{1}C_{2}+R_{1}R_{2}C_{2}C_{2}+s^{2}L_{2}C_{2}+s^{2}L_{2}C_{2}+s^{2}L_{2}C_{2}}\right]\right]$$

$$=V_{1} \\ \times \left[r_{1}R_{2}C_{2}C_{2}+R_{1}C_{1}L_{2}C_{2}+R_{1}C_{1}+L_{1}C_{2}+s^{3}(R_{2}L_{1}C_{2}C_{2}+R_{2}L_{1}C_{1}C_{2}+R_{2}L_{1}C_{1}C_{2}+R_{2}L_{1}C_{1}C_{2}+R_{2}L_{1}C_{1}C_{2}+R_{2}L_{1}C_{1}C_{2}+R_{2}L_{1}C_{1}C_{2}+R_{2}L_{1}C_{1}C_{2}+R_{2}L_{2}C_{2}+s^{2}L_{2}C_{2}+s^{2}L_{2}C_{2}+s^{2}L_{2}C_{2}\right]\right]$$

$$(13)$$

Therefore, output voltage  $V_2$  of the aggressor trace with victim trace grounded ( $V_3=0$ ) is given by equation (14).  $V_2 = V_1 * \frac{1 + sR_2(C_c + C_2) + s^2L_2(C_c + C_2)}{(1 + s(R_1C_1 + R_2C_2 + R_1C_c + R_2C_c) + s^2(L_1(C_c + C_1C_c + C_1C_2) + L_2(C_2 + C_1C_c + C_1C_2))} + s^3(R_2L_1(C_2C_c + C_1C_c + C_1C_2) + R_1L_2(C_2C_c + C_1C_c + C_1C_2)) + s^4(L_1L_2(C_2C_c + C_1C_c + C_1C_2))$  (14)

The crosstalk voltage, FEXT ( $V_4$ ) at the end of victim trace because of coupling of aggressor trace is calculated as follows. Here equation (12) can be is re-written as:

$$V_{2} = V_{4} * \frac{\left(1 + sR_{2}C_{C} + sR_{2}C_{2} + s^{2}L_{2}C_{C} + s^{2}L_{2}C_{C}\right)}{\left(sR_{2}C_{C} + s^{2}L_{2}C_{C}\right)}$$

Substitute value of  $V_2$  in equation (10) to obtain the theoretical expression for crosstalk voltage FEXT ( $V_4$ ) on the victim trace.

$v_{4} \left[ \frac{\left(1 + sR_{2}C_{c} + sR_{2}C_{2} + s^{2}L_{2}C_{c} + s^{2}L_{2}C_{2}\right)}{\left(sR_{2}C_{c} + s^{2}L_{2}C_{c}\right)} \right] \left[ \left(1 + sR_{1}C_{c} + sR_{1}C_{1} + s^{2}L_{1}C_{c} + s^{2}L_{1}C_{1}\right) \right] = v_{1} + v_{4} \left(sR_{1}C_{c} + s^{2}L_{1}C_{c}\right)$ FEXT (V<sub>4</sub>) is derived as in equation (15).

$\frac{1}{2} \sum_{k=1}^{n} \frac{1}{k} \sum_{k=1}^{n} \frac{1}$

$$V_{4} = V_{1} * \frac{1}{(1 + s(R_{1}C_{1} + R_{2}C_{2} + R_{1}C_{c} + R_{2}C_{c}) + s^{2}(L_{1}(C_{c} + C_{1}) + R_{1}R_{2}(C_{2}C_{c} + C_{1}C_{c} + C_{1}C_{2}) + L_{2}(C_{2} + C_{c}))} + s^{3}(R_{2}L_{1}(C_{2}C_{c} + C_{1}C_{c} + C_{1}C_{2}) + R_{1}L_{2}(C_{2}C_{c} + C_{1}C_{c} + C_{1}C_{2})) + s^{4}(L_{1}L_{2}(C_{2}C_{c} + C_{1}C_{c} + C_{1}C_{2}))$$

$$Similarly, the constant constant for a co$$

Similarly, theoretical expression for crosstalk voltage NEXT  $(V_3)$  is derived as in equation (16).

$$V_{3} = \frac{C_{c}}{(C_{c} + C_{2}) + sR_{1}(C_{1}C_{2} + C_{1}C_{c} + C_{2}C_{c}) + s^{2}L_{1}(C_{1}C_{2} + C_{2}C_{c} + C_{1}C_{c})}$$

(16)

#### A. Transient Analysis of Coupled RLC Interconnect

The transient analysis objective is to evaluate the amount of crosstalk voltage injected on to victim trace due to both capacitive and inductive coupling. During analysis, RLC interconnect/ trace is assumed as a microstrip on a multilayer PCB of length L=3 inch, width W=8.0 mils, Dielectric height H=6.0 mils with a dielectric constant  $\varepsilon_r = 4.3$ . The characteristic impedance of trace is  $Z_0=50\Omega$  and the delay through the trace is  $t_d=448$  ps. The trace element parameters are: R<sub>1</sub>=15Ω, R<sub>2</sub>=15Ω, C<sub>1</sub>=C<sub>2</sub>=9.0pF, C<sub>C</sub>=2.0pF, L<sub>1</sub>=L<sub>2</sub>=22.5nH, K=0.2.

Therefore with these parameters the output voltage  $V_2$  obtained on the aggressor line is given in equation (17).

$$\frac{V_2}{V_1} = \frac{2.475e \cdot 19s^2 + 1.65e \cdot 10s + 1}{5.923e \cdot 38s^4 + 7.897e \cdot 29s^3 + 5.213e \cdot 19s^2 + 3.3e \cdot 10s + 1}$$

(17)

Crosstalk voltage FEXT, on Victim is given in equation (18).

$$\frac{V_4}{V_1} = \frac{4.5e \cdot 20s^2 + 3e \cdot 11s + 1}{5.923e \cdot 38s^4 + 7.897e \cdot 29s^3 + 5.213e \cdot 19s^2 + 3.3e \cdot 10s + 1}$$

(18)

Crosstalk voltage NEXT, on Victim is given in equation (19).

$$\frac{V_3}{V_1} = \frac{2e - 12}{2.632e - 30s^2 + 1.755e - 21s + 1.1e - 11}$$

(19)

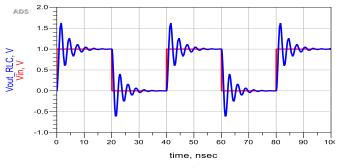

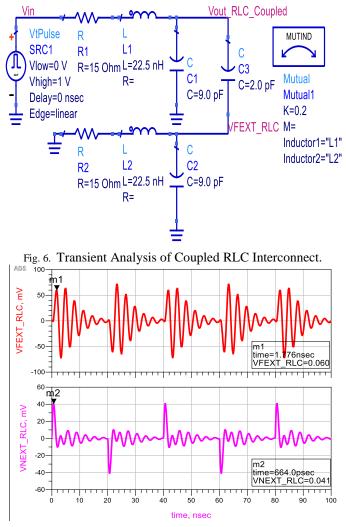

The transient analysis of two 3 inches coupled RLC trace/interconnects shown in Fig.6. is performed for a rising, falling edge-rates of 50ps respectively. A pulse is applied on the aggressor trace  $(V_1)$  with victim trace  $(V_3=0)$  as grounded.

V

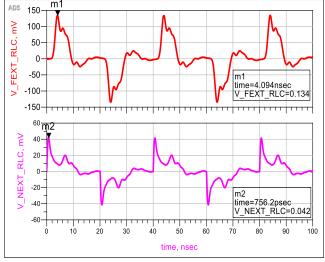

Fig. 7. FEXT and NEXT Response of Coupled RLC Interconnect.

Figure.7 shows the crosstalk voltage response of a coupled RLC respectively because of the affect of aggressor on to the victim trace. FEXT voltage is  $\approx$  133 mV peak-to-peak and NEXT voltage  $\approx$  52 mV peak-to-peak. FEXT voltage (>100 mV) could cause several signal integrity problems.

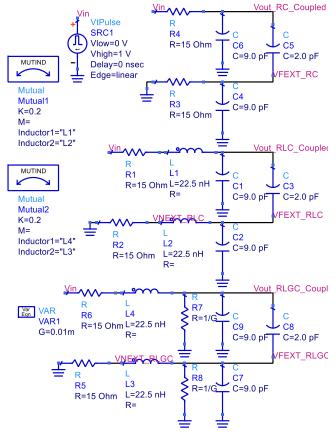

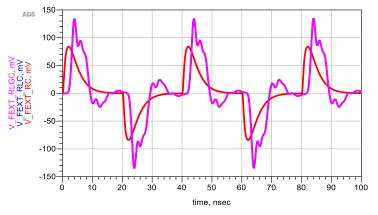

Fig. 8. Transient Analysis of Coupled RC, RLC and RLGC Interconnects.

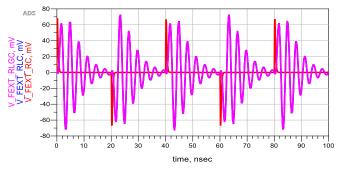

The transient analysis of all coupled RC, RLC and RLGC trace/interconnects is shown in Fig.8. Crosstalk voltage FEXT response of RC, RLC and RLGC trace is shown in Fig.9.

Fig. 9. FEXT Response of Coupled RC, RLC and RLGC Interconnects.

B. Effect of Mutual Inductance (M) on Coupled Inductors

At high frequencies, reactive component inductance(L) creates numerous signal integrity problems i.e. ringing due to inductive coupling. The inductors  $L_1$  and  $L_2$  are coupled with coupling coefficient K (0< K <1) so as to obtain minimum crosstalk.

$$K = \frac{M}{\sqrt{L1 * L2}} \tag{20}$$

An extra inductance gets added because of the coupling between the inductor coils  $L_1$  and  $L_2$  and is called as mutual inductance (M).

$$L_T = L_1 + L_2 + M$$

$$M = K^* \sqrt{L_1 * L_2}$$

(21)

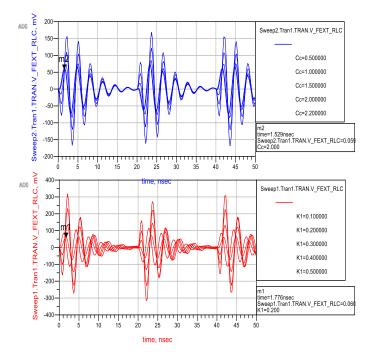

Fig. 10. Response for different values of K and C<sub>C</sub> on Coupled Interconnects.

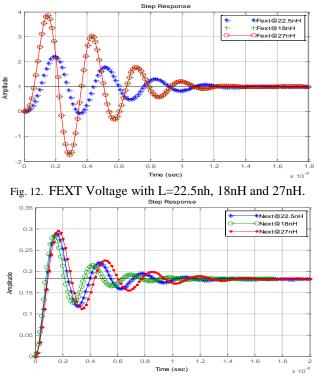

Parametric simulation response of 3 inch coupled RLC trace for different values of coupling coefficient (K=0.1:0.1:0.5) and coupling capacitor ( $C_c$ =0.5:0.5:2.2) is shown in Fig.10. This helps to find the optimal values of K and  $C_c$  so that the crosstalk voltage FEXT, on the victim trace is as low as possible. From the simulation result it is evident that for K=0.2 and  $C_c$ =2.0pF the crosstalk voltages on the victim trace is low. In a 3 inch coupled RLC trace inductors  $L_1$  and  $L_2$  are coupled through a mutual inductance (M) which adds an extra inductance on to interconnect. In order to observe the effects of M on  $L_1$  and  $L_2$  two test cases have been considered. The step response for output voltage, FEXT and NEXT voltage response respectively with selected optimum values of K=0.2,  $C_c$ =2.0pF and  $L_1$ =L<sub>2</sub>=22.5nH, M=4.5nH are shown in Fig.11, Fig.12 and Fig.13.

Case (i): (L1-M) and (L<sub>2</sub>-M) = (22.5nH-4.5nH) = 18nH

$$\frac{V_2}{V_1} = \frac{1.98e - 19s^2 + 1.65e - 10s + 1}{3.79e - 38s^4 + 6.32e - 29s^3 + 4.22e - 19s^2 + 3.3e - 10s + 1}$$

$$\frac{V_4}{V_1} = \frac{1.2e - 09s^2 + s}{3.79e - 38s^4 + 6.32e - 29s^3 + 4.22e - 19s^2 + 3.3e - 10s + 1}$$

$$\frac{V_3}{V_1} = \frac{1.82e - 01}{1.91e - 19s^2 + 1.6e - 10s + 1}$$

Case (ii): (L1+M) and (L<sub>2</sub>+M) = (22.5nH+4.5nH) = 27nH

$$\frac{V_2}{V_1} = \frac{2.97e - 19s^2 + 1.65e - 10s + 1}{8.53e - 38s^4 + 9.48e - 29s^3 + 6.2e - 19s^2 + 3.3e - 10s + 1}$$

$$\frac{V_3}{V_1} = \frac{1.82e - 001}{2.87e - 019s^2 + 1.6e - 010s + 1}$$

$$\frac{V_3}{V_1} = \frac{1.82e - 001}{2.87e - 019s^2 + 1.6e - 010s + 1}$$

$$\frac{V_3}{V_1} = \frac{1.82e - 001}{2.87e - 019s^2 + 1.6e - 010s + 1}$$

$$\frac{V_4}{V_4} = \frac{V_4}{V_{404} + 1000} = \frac{1.82e - 001}{2.87e - 019s^2 + 1.6e - 010s + 1}$$

$$\frac{V_4}{V_4} = \frac{V_4}{V_{404} + 1000} = \frac{1.82e - 001}{2.87e - 019s^2 + 1.6e - 010s + 1}$$

$$\frac{V_4}{V_4} = \frac{V_4}{V_{404} + 1000} = \frac{1.82e - 001}{2.87e - 019s^2 + 1.6e - 010s + 1}$$

$$\frac{V_4}{V_4} = \frac{V_4}{V_{404} + 1000} = \frac{1.82e - 001}{2.87e - 019s^2 + 1.6e - 010s + 1}$$

$$\frac{V_4}{V_4} = \frac{V_4}{V_{404} + 1000} = \frac{V_4}{V_{404} + 1000} = \frac{1.82e - 001}{V_{404} + 1000} = \frac{1.82e - 000}{V_{404} + 1000} = \frac{1.82e - 000}{V_{404} + 1000} = \frac{1.82e - 000}{V_{404} + 1000} =$$

Fig. 11. Analysis of Vout with L=22.5nh, 18nH and 27nH.

Fig. 13. NEXT Voltage with L=22.5nh, 18nH and 27nH.

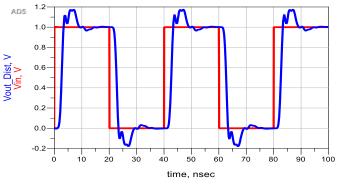

Fig. 14. Transient Analysis of Distributed model of RLC interconnect.

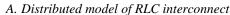

The transient analysis of distributed model of RLC trace/interconnects is obtained by cascading of lumped RLC is shown in Fig.14. RLC interconnect/ trace is on a PCB is assumed as a microstrip of length L=5\*3 inch=15 inches, width W=8.0 mils, Dielectric height H=6.0 mils with a dielectric constant  $\mathcal{E}_r = 4.3$ .Simulation response is shown in Fig.15, which shows that the delay and time of flight have increased when compared with result in Fig.3. A comparison of lumped RLC and distributed RLC models is listed in Table II.

Fig. 15. Transient Analysis of Distributed model of RLC interconnect.

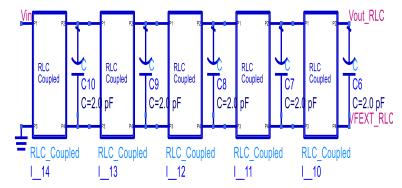

B. Distributed Coupled RLC interconnect model

Fig. 16. Transient Analysis of Distributed Coupled RLC model.

Transient Analysis of microstip trace of coupled length L=5\*3 inch=15 inches, width W=8.0 mils, Dielectric height H=6.0 mils with a dielectric constant  $\mathcal{E}_r = 4.3$  on a multilayer PCB is shown in Fig.16. The two traces are coupled through capacitive coupling Cc=2.0pF.The transient response for output voltage and crosstalk voltages FEXT and NEXT are shown in Fig.17 and Fig.18.

Fig. 17. Transient Response of Distributed model of Coupled RLC.

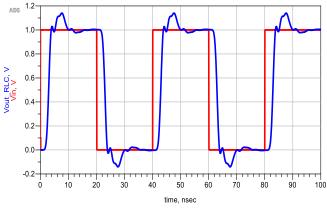

FEXT voltage is  $\approx 268 \text{ mV}$  peak-to-peak and NEXT voltage  $\approx 84 \text{ mV}$  peak-to-peak. Typically, FEXT voltage (>100 mV) could cause several signal integrity problems.

Fig. 18. FEXT and NEXT Response of Distributed Coupled RLC Interconnect.

Figure.19 and Table-I shows the crosstalk voltage FEXT response of all the distributed coupled models of RC, RLC and RLGC trace/interconnects with microstrip parameters.

Fig. 19. FEXT Response of Distributed Coupled RC, RLC and RLGC Interconnect.

| TABLE I. | COMPARISON OF | CROSSTALK VOLTA | GES OF COUPLED | INTERCONNECTS. |

|----------|---------------|-----------------|----------------|----------------|

|----------|---------------|-----------------|----------------|----------------|

| Type of | Lumped Coupled |       | <b>Distributed Coupled</b> |       |  |

|---------|----------------|-------|----------------------------|-------|--|

| Models  | Мо             | dels  | Models                     |       |  |

|         | VNEXT          | VFEXT | VNEXT                      | VFEXT |  |

|         | (mV)           | (mV)  | (mV)                       | (mV)  |  |

| RC      | 0              | 134   | 80                         | 168   |  |

| RLC     | 52             | 133   | 84                         | 268   |  |

| RLGC    | 51             | 133   | 82                         | 268   |  |

Table I lists the comparison of crosstalk voltages FEXT and NEXT for coupled models of RLC trace/interconnects in a transient analysis.

|      | Lumped Models |                          |                     | Distributed Models |                              |                     |

|------|---------------|--------------------------|---------------------|--------------------|------------------------------|---------------------|

|      | Delay<br>(ps) | Avg<br>Powe<br>r<br>(uW) | PDP<br>(Joule<br>s) | Dela<br>y<br>(ns)  | Avg<br>Pow<br>er<br>(mW<br>) | PDP<br>(Joul<br>es) |

| RC   | 338.0<br>0    | 255.0<br>0               | 8.619<br>e-14       | 4.17               | 1.33                         | 5.546<br>e-12       |

| RLC  | 778.6<br>2    | 319.2<br>0               | 2.485<br>e-13       | 3.315              | 1.33<br>7                    | 4.434<br>e-12       |

| RLGC | 778.7<br>8    | 324.2<br>5               | 2.525<br>e-13       | 3.317              | 1.36<br>3                    | 4.521<br>e-12       |

TABLE II. COMPARISON OF DELAYS AND POWER IN INTERCONNECTS.

TABLE III. COMPARISON OF DELAYS AND POWER IN COUPLED INTERCONNECTS.

|      | Coupled Lumped<br>Models |                          | Coupled Distributed<br>Models |               |                              |                     |

|------|--------------------------|--------------------------|-------------------------------|---------------|------------------------------|---------------------|

|      | Delay<br>(ps)            | Avg<br>Powe<br>r<br>(uW) | PDP<br>(Joul<br>es)           | Delay<br>(ns) | Avg<br>Powe<br>r<br>(mW<br>) | PDP<br>(Joul<br>es) |

| RC   | 394.2<br>6               | 314.6<br>1               | 1.240<br>e-13                 | 5.017         | 1.631                        | 8.185<br>e-12       |

| RLC  | 845.8<br>6               | 296.5<br>8               | 2.508<br>e-13                 | 3.844         | 1.660                        | 6.381<br>e-12       |

| RLGC | 846.0<br>2               | 302.6<br>3               | 2.560<br>e-13                 | 3.848         | 1.684                        | 6.480<br>e-12       |

The length of the trace/interconnects also determines the delay and timing of output signal. The amount of delay for a given length (L) varies from layer to layer on a multilayer PCB. Table II lists the comparison of delay, average power and power delay product (PDP) in lumped, distributed models. Table III lists the comparison of coupled lumped models and coupled distributed models of interconnects with SPICE simulation.

#### V. CONCLUSION

In this paper, an approach for modeling and analysis of crosstalk noise voltage in a coupled model of RLC trace/ interconnect is proposed. This is used to determine the crosstalk coupling effect between the two on-chip traces viz: aggressor and a victim trace. The effect of inductive cross-talk, capacitive crosstalk, and coupling are considered for various combinations coupling coefficient (K) and Cc on the aggressor and victim lines. Characterizations of all models of RLGC traces in time domain are performed with properties of microstrip (as trace) on a multilayer PCB. In the transient analysis crosstalk voltage metrics FEXT, NEXT are measured and compared for each coupled model of interconnects. The modeling approach can be used for fast estimation of crosstalk voltages in coupled traces. A detailed SPICE analysis of all RC, RLC and RLGC trace models are performed for propagation delays, average power and power delay products (PDP). A comparison of all models of interconnects with metrics are listed in tables.

#### REFERENCES

- [1] Semiconductor Industries Association (SIA), International Technology Roadmap for Semiconductors (ITRS), 2007.

- [2] Chen Wei, Huang Qiu-yuan, Zhou Peng, "Signal Integrity Analysis and Design in High Speed Circuit M" in PHEI, Beijing:, pp. 25-36, 2009.

- [3] JianQiang Mo, "High-speed Digital Circuit Signal Integrity Analysis", Electronic Test, vol. 9, no. 9, pp. 5-9, 2011.

- [4] A.B.Khang, S.Muddu, "An Analytical Delay Model for RLC Interconnects", IEEE Trans. Computer Aided Design 16(12) 1507-1514, 1997.

- [5] Y. I. Ismail, E. G. Friedman, and J. L. Neves, "Equivalent Elmore delay for RLC trees," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 19, no. 1, pp. 83–97, Jan. 2000.

- [6] Vikas Maheshwari, Abhishek Sharma, R.Kar, "Transient and Delay Analysis for On-Chip High Speed VLSI RLCG Global Interconnect for Unit Impulse Input", IEEE, Conference on Research and Development, 2011.

- [7] Rajib Kar, A. K. Bhattacharjee ,Vikas Maheshwari " Delay Model for VLSI RLCG Global Interconnects", IEEE, PRIMEASIA, 2012.

- [8] Sourajeet Roy, Anestis Dounavis, "Efficient Delay and Crosstalk Modeling of RLC Interconnects Using Delay Algebraic Equations", IEEE Trans. On VLSI Systems, vol.19, no.2, 2011.

- [9] Muhammad Sanaullah and Masud H. Chowdhury, "Analysis of RLC Interconnect Delay Model using Second Order Approximation" IEEE, Symposium Circuits and Systems, 2014.

- [10] Sunil Jadav, Rajeevan Chandel Munish Vashishath "A Superior Delay Estimation Model for VLSI Interconnect in Current Mode Signaling", World Academy of Science, Engineering and Technology, 2015.

- [11] Mustafa Celik, Lawrence Pileggi, Altan Odabasioglu "IC Interconnect Analysis ", 2002.